Điện tử số

Điện tử số

I hệ đếm

+ hệ có trọng số: vd hệ 10,..,,,, Hệ không có trọng số: hệ la mã

+ Tham số : cơ số, trọng số, giá trị = cơ số mũ trọng số

cơ số là số ký tự biểu diễn( hệ 10 là 10), trọng số là vị trí( hàng chục,..)

+ chuyển phần dư từ hệ 10 -> hệ 2:

vd: 0,3125 * 2= 0,625 => thập phân: 0,625 ,,, nguyên: 0

0,625 * 2 = .................................0,25......................... 1

0,25...............................................0,5 ......................... 0

0,5..................................................0............................ 1

+ Hệ nhị phân: Msb: bit có trọng số cao nhất, Lsb: ... thấp nhất(0)

+ Biểu diễn số nguyên có dấu: Msb= 0: số +,,, Msb=1 số -

Msb= 0 biểu diễn bình thường

Msb= 1 ............= giá trị âm của số bù 2 = số bù 1(đảo bít) cộng 1

( biểu diễn số bù 2 mặc định là số nguyên +)

+ Các hệ mã: nhị p, BCD(nhị phân chỉ bd từ 0-9), dư 3(BCD + 3 đơn vị), Gray

+ Gray: 2 từ mã cạnh nhau hay đối xứng nhau chỉ != 1 bít

vd: 000; 001: 011; 010; 110; 111; 101; 100 (chú ý thứ tự tăng: maximum không thể tăng mới giảm)

+ Chuyển mã Nhị Phân sang Gray và ngược lại (đợi hình vẽ)

CHương 2: Hàm Logic và Cổng Logic

1 Các hàm logic cơ bản

+ biến logic: biển của 1 hàm chỉ nhận giá trị 0 hoặc 1

+ hàm logic: hàm của các biến logic, ham f chỉ nhận 2 giá trị 0;1

ví dụ: chờ hình ảnh

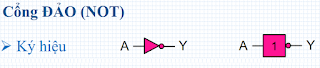

+ gồm: AND, OR, XOR, NOT, NOT- AND, NOT- OR, NOT- XOR

2 Các tính chất

+ giao hoán + kết hợp

+ Phân phối:

+ A.A....A=A + A+A+..+A=A

+ phép đảo, tuyển, và với 0,1

+ Định luật De-Morgan: đảo của các tuyển = hội của các đảo...

+ Quy tắc thay thế: phải thay thế tương ứng ở cả 2 bên

+ Quy tắc đối ngẫu: nếu thay thế cả 2 bên: cứ phép + thành phép nhân và ngược lại, 0 thành 1 và ngược lại, giá trị ko đổi

+ tính chất XoR:

3 Các cổng Logic (7 cổng ứng 7 hàm logic cơ bản)

+ kn: là mạch điện tạo các linh kiện bán dẫn, thực hiện chức năng hàm logic cơ bản, đầu vào: th mức thấp( =0) và cao(=1)

+ hình vẽ 7 cổng sau:

3 Biểu diễn hàm logic

3,1 Biểu diễn bằng bảng giá trị hàm ((n+1) cột, 2^n+ 1 hàm)

3,2 ...................... biểu thức đại số

+ Tích, Tổng đầy đủ:

+ Dạng chuẩn tắc tuyển, hội:

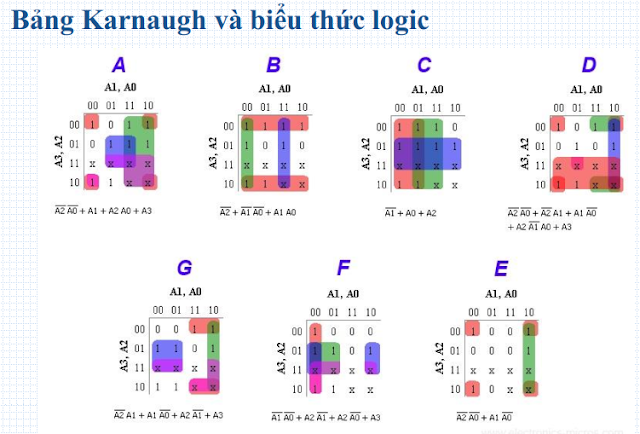

3,3 ...................... Bảng Karnaugh

3,4 Sơ đồ mạch

4 Tối thiểu hàm logic

4.1 Phương pháp đại số

4.2 Phương pháp bảng karnaugh

=> hình trên cùng trái: loại cái có 2 giá trị 0,1 => C đảo

4.3 Phương pháp MC- Cluskey

Chương 3: Vi Mạch Số (IC)

+ Nhiều mạch logic-> (kết hợp) Module-> Chíp: xử nhiều bt

1 KN: Integrated Circuit (IC) là tập các mạch điện chứa linh kiện bán dẫn(transitor) và linh kiện điện tử thụ động( điện trở) được kết nối với nhau để thực hiện chức năng xác định

+ Ưu điểm: giảm thể tích, giá,.. tăng tuổi thọ, ít tiêu thụ năng lượng

+ Nhược điểm: yeu cầu độ ổ định của nguồn điện

2 Phân Loại:

+ Theo bản chất tín hiệu:

+ Theo mật độ tích hợp:

+ Theo công nghệ chế tạo: ........

3 Các tham số cơ bản của IC

4 Một số IC thông dụng

4.1 IC họ TTL

4.2 IC họ MOSFET

................ còn nhiều nữa......................

Chương 4: Mạch Tổ Hợp

I Kiến thức chung

1,Giới thiệu:

+ mạch tổ hợp là 1 mạch số ghép các phép toán logic=> thực hiện 1 bài toán: có các tín hiệu đầu vào và đầu ra

2 Các phương trình mạch tổ hợp

3 Phương pháp biểu diễn:

II Tổng hợp Mạch tổ hợp

1 Các bước:

2 Tổng hợp mạch 1 đầu ra

3 Tổng hợp mạch nhiều đầu ra

III Phân tích mạch tổ hợp

1 Phân tích tĩnh

Chuyển từ mã nhị phân sang mã dư 3

2 Phân tích động

2.1 Hazard tĩnh

2.2 Hazard động

2.3 Các biện pháp khắc phục

IV Các mạch giải mã thông dụng

1 Bộ mã hóa/ giải mã

+ Giải mã nhị phân

+ Giải mã BCD-> mã 7 đoạn

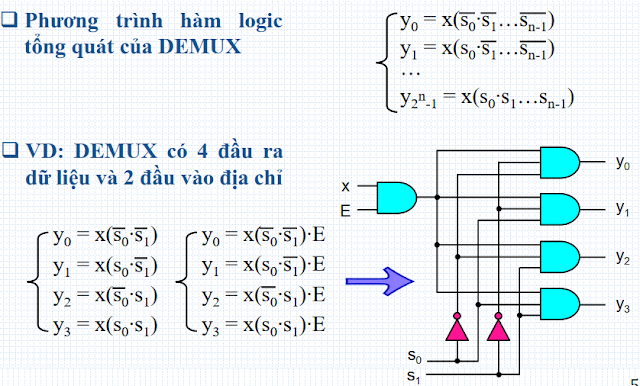

2 Bộ dồn kênh/ phân kênh (Mux, DeMux)

+ MUX:

+ DEMUX:

3 Mạch phép toán số học

+ Bộ cộng nhị phân

- HA( cộng không nho)

- FA ( cộng có nhớ)

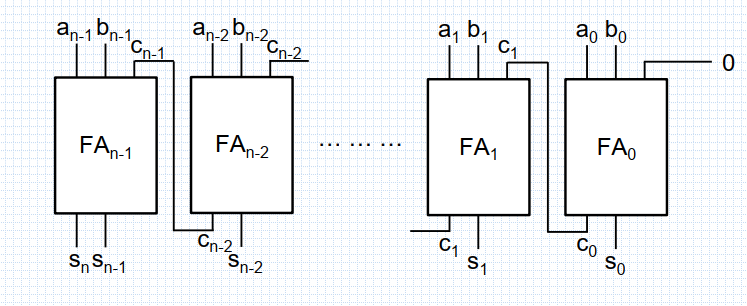

+ Bộ cộng 2 số nhị phân nhiều bít

Cách 1: từ các bộ cộng FA song song:

-> thằng đằng trước phải chờ thằng đằng sau => quá nhiều thời gian => xây dựng mạch cộng thấy trước nhớ

Cách 2: Carry Look-ahead Adder(CLA)

4.3.2 Bộ trừ nhị phân

+ Mạch trừ 1 bít không nhớ (HS)

+ Mạch trừ 1 bít có nhớ (FS)

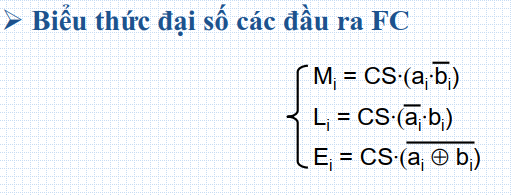

+ Mạch so sánh 2 bít đầy đủ (FC): so sánh 2 số nhị phân 1 bít

+ Mạch so sánh đầy đủ 2 số nhị phân: ghép các bộ FC lại, sử dụng thêm tín hiệu chọn chip CS (CS=0 => tất cả đầu ra FC bằng 0)

Chương 5: Mạch tuần tự

I KT Chung

I.1 Định nghĩa mạch tuần tự

+ là một mạch số có tổ hợp tín hiệu ra tại một thời điểm phụ thuộc: vào tín hiệu vào, và cả trạng thái trước của tín hiệu này

=> Để thực hiện mạch tuần tự: phải có phần tử nhớ + 1 số phần tử logic cơ bản

I.2 Các mô hình mạch tuần tự

+ Mô hình kỹ thuật

+ Mô hình toán học

I.3 Các phương pháp mô tả

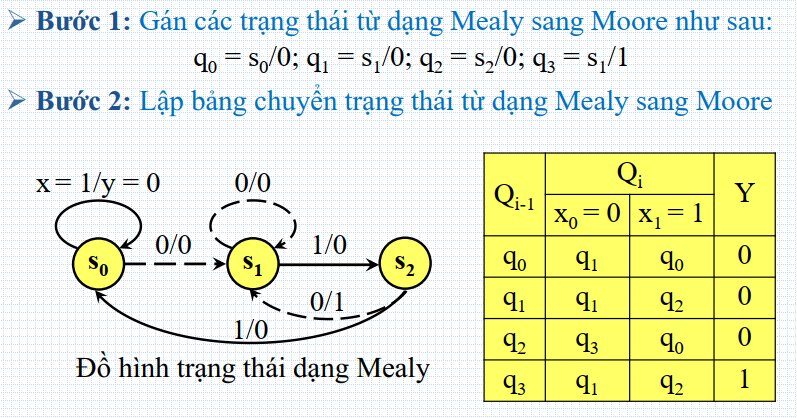

I.4 Chuyển đổi MMT dạng Mealy và Moore

+ Ví dụ:

=> Chuyển sang dạng Moore

I.5 Phân loại mạch tuần tự

+ Mạch tuần tự đồng bộ

+ Mạch tuần tự không đồng bộ

II Phần tử nhớ

II.1 Khái niệm

+ Dùng để nhớ các trạng thái trong của mạch( 0 hoặc 1)

+ được xd từ các cổng logic cơ bản nhưng do vai trò quan trọng nên có ký hiệu và cách biểu diễn riêng

+ Hai dạng phần tử nhớ: Latch(chốt) đồng bộ theo mức và Flip- Flop đồng bộ theo sườn

II.2 Các phần tử nhớ cơ bản

2.1 SR Flip FLop

2.2 JK Flip Flop

2.3 D Flip Flop

2.4 T Flip Flop

II.3 Các phương pháp đồng bộ

3.1 Đồng bộ theo mức

3.2 Đồng bột theo sườn

II.4 Xác định đầu vào kích của Flip Flop

II.5 Xây dựng Flip FLop khác

I hệ đếm

+ hệ có trọng số: vd hệ 10,..,,,, Hệ không có trọng số: hệ la mã

+ Tham số : cơ số, trọng số, giá trị = cơ số mũ trọng số

cơ số là số ký tự biểu diễn( hệ 10 là 10), trọng số là vị trí( hàng chục,..)

+ chuyển phần dư từ hệ 10 -> hệ 2:

vd: 0,3125 * 2= 0,625 => thập phân: 0,625 ,,, nguyên: 0

0,625 * 2 = .................................0,25......................... 1

0,25...............................................0,5 ......................... 0

0,5..................................................0............................ 1

+ Hệ nhị phân: Msb: bit có trọng số cao nhất, Lsb: ... thấp nhất(0)

+ Biểu diễn số nguyên có dấu: Msb= 0: số +,,, Msb=1 số -

Msb= 0 biểu diễn bình thường

Msb= 1 ............= giá trị âm của số bù 2 = số bù 1(đảo bít) cộng 1

( biểu diễn số bù 2 mặc định là số nguyên +)

+ Các hệ mã: nhị p, BCD(nhị phân chỉ bd từ 0-9), dư 3(BCD + 3 đơn vị), Gray

+ Gray: 2 từ mã cạnh nhau hay đối xứng nhau chỉ != 1 bít

vd: 000; 001: 011; 010; 110; 111; 101; 100 (chú ý thứ tự tăng: maximum không thể tăng mới giảm)

+ Chuyển mã Nhị Phân sang Gray và ngược lại (đợi hình vẽ)

CHương 2: Hàm Logic và Cổng Logic

1 Các hàm logic cơ bản

+ biến logic: biển của 1 hàm chỉ nhận giá trị 0 hoặc 1

+ hàm logic: hàm của các biến logic, ham f chỉ nhận 2 giá trị 0;1

ví dụ: chờ hình ảnh

+ gồm: AND, OR, XOR, NOT, NOT- AND, NOT- OR, NOT- XOR

2 Các tính chất

+ giao hoán + kết hợp

+ Phân phối:

+ A.A....A=A + A+A+..+A=A

+ phép đảo, tuyển, và với 0,1

+ Định luật De-Morgan: đảo của các tuyển = hội của các đảo...

+ Quy tắc thay thế: phải thay thế tương ứng ở cả 2 bên

+ tính chất XoR:

3 Các cổng Logic (7 cổng ứng 7 hàm logic cơ bản)

+ kn: là mạch điện tạo các linh kiện bán dẫn, thực hiện chức năng hàm logic cơ bản, đầu vào: th mức thấp( =0) và cao(=1)

+ hình vẽ 7 cổng sau:

3 Biểu diễn hàm logic

3,1 Biểu diễn bằng bảng giá trị hàm ((n+1) cột, 2^n+ 1 hàm)

3,2 ...................... biểu thức đại số

+ Tích, Tổng đầy đủ:

+ Dạng chuẩn tắc tuyển, hội:

3,3 ...................... Bảng Karnaugh

3,4 Sơ đồ mạch

4 Tối thiểu hàm logic

4.1 Phương pháp đại số

4.2 Phương pháp bảng karnaugh

=> hình trên cùng trái: loại cái có 2 giá trị 0,1 => C đảo

4.3 Phương pháp MC- Cluskey

Chương 3: Vi Mạch Số (IC)

+ Nhiều mạch logic-> (kết hợp) Module-> Chíp: xử nhiều bt

1 KN: Integrated Circuit (IC) là tập các mạch điện chứa linh kiện bán dẫn(transitor) và linh kiện điện tử thụ động( điện trở) được kết nối với nhau để thực hiện chức năng xác định

+ Ưu điểm: giảm thể tích, giá,.. tăng tuổi thọ, ít tiêu thụ năng lượng

+ Nhược điểm: yeu cầu độ ổ định của nguồn điện

2 Phân Loại:

+ Theo bản chất tín hiệu:

+ Theo mật độ tích hợp:

+ Theo công nghệ chế tạo: ........

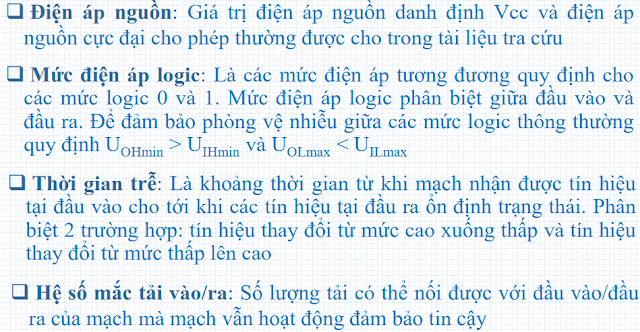

3 Các tham số cơ bản của IC

4 Một số IC thông dụng

4.1 IC họ TTL

4.2 IC họ MOSFET

................ còn nhiều nữa......................

Chương 4: Mạch Tổ Hợp

I Kiến thức chung

1,Giới thiệu:

+ mạch tổ hợp là 1 mạch số ghép các phép toán logic=> thực hiện 1 bài toán: có các tín hiệu đầu vào và đầu ra

2 Các phương trình mạch tổ hợp

3 Phương pháp biểu diễn:

II Tổng hợp Mạch tổ hợp

1 Các bước:

2 Tổng hợp mạch 1 đầu ra

3 Tổng hợp mạch nhiều đầu ra

III Phân tích mạch tổ hợp

1 Phân tích tĩnh

Chuyển từ mã nhị phân sang mã dư 3

2 Phân tích động

2.1 Hazard tĩnh

2.2 Hazard động

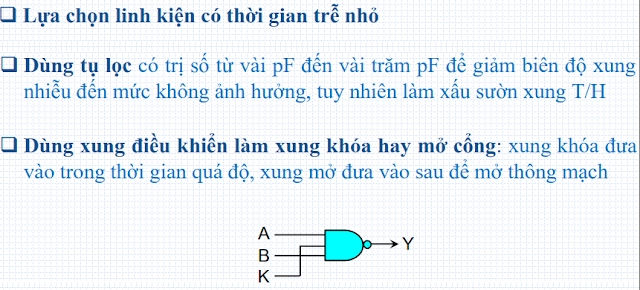

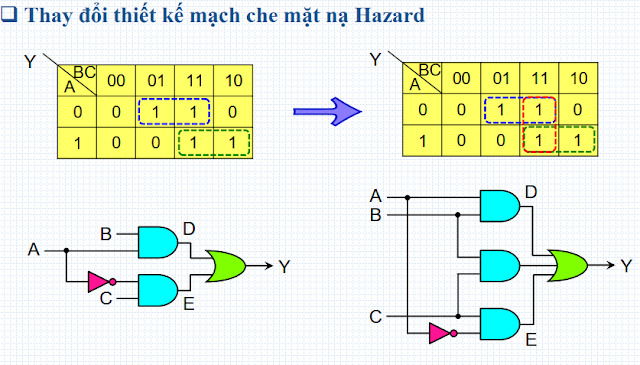

2.3 Các biện pháp khắc phục

IV Các mạch giải mã thông dụng

1 Bộ mã hóa/ giải mã

+ Giải mã nhị phân

+ Giải mã BCD-> mã 7 đoạn

2 Bộ dồn kênh/ phân kênh (Mux, DeMux)

+ MUX:

+ DEMUX:

3 Mạch phép toán số học

+ Bộ cộng nhị phân

- HA( cộng không nho)

- FA ( cộng có nhớ)

+ Bộ cộng 2 số nhị phân nhiều bít

Cách 1: từ các bộ cộng FA song song:

-> thằng đằng trước phải chờ thằng đằng sau => quá nhiều thời gian => xây dựng mạch cộng thấy trước nhớ

Cách 2: Carry Look-ahead Adder(CLA)

4.3.2 Bộ trừ nhị phân

+ Mạch trừ 1 bít không nhớ (HS)

+ Mạch trừ 1 bít có nhớ (FS)

+ Mạch so sánh 2 bít đầy đủ (FC): so sánh 2 số nhị phân 1 bít

+ Mạch so sánh đầy đủ 2 số nhị phân: ghép các bộ FC lại, sử dụng thêm tín hiệu chọn chip CS (CS=0 => tất cả đầu ra FC bằng 0)

Chương 5: Mạch tuần tự

I KT Chung

I.1 Định nghĩa mạch tuần tự

+ là một mạch số có tổ hợp tín hiệu ra tại một thời điểm phụ thuộc: vào tín hiệu vào, và cả trạng thái trước của tín hiệu này

=> Để thực hiện mạch tuần tự: phải có phần tử nhớ + 1 số phần tử logic cơ bản

I.2 Các mô hình mạch tuần tự

+ Mô hình kỹ thuật

+ Mô hình toán học

I.3 Các phương pháp mô tả

I.4 Chuyển đổi MMT dạng Mealy và Moore

+ Ví dụ:

=> Chuyển sang dạng Moore

I.5 Phân loại mạch tuần tự

+ Mạch tuần tự đồng bộ

+ Mạch tuần tự không đồng bộ

II Phần tử nhớ

II.1 Khái niệm

+ Dùng để nhớ các trạng thái trong của mạch( 0 hoặc 1)

+ được xd từ các cổng logic cơ bản nhưng do vai trò quan trọng nên có ký hiệu và cách biểu diễn riêng

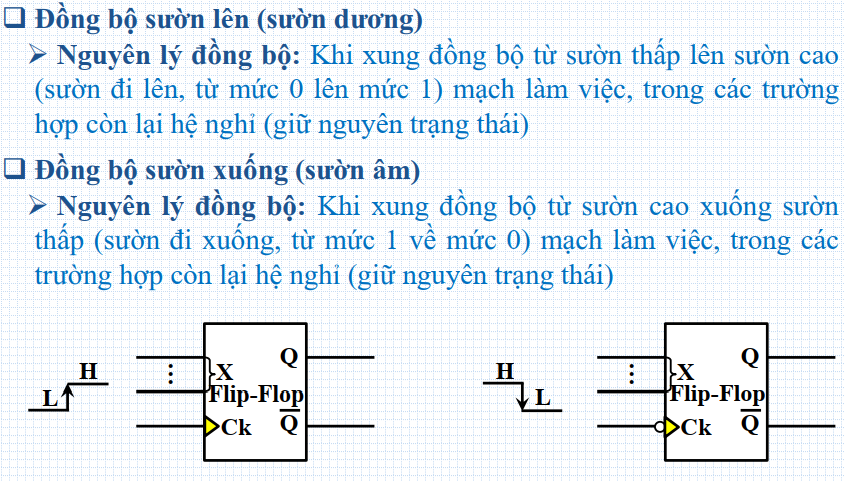

+ Hai dạng phần tử nhớ: Latch(chốt) đồng bộ theo mức và Flip- Flop đồng bộ theo sườn

II.2 Các phần tử nhớ cơ bản

2.1 SR Flip FLop

2.2 JK Flip Flop

2.3 D Flip Flop

2.4 T Flip Flop

II.3 Các phương pháp đồng bộ

3.1 Đồng bộ theo mức

3.2 Đồng bột theo sườn

II.4 Xác định đầu vào kích của Flip Flop

II.5 Xây dựng Flip FLop khác

Nhận xét

Đăng nhận xét